1 Foundational Technology Layers

1.1

Process Technology, Equipment, Materials And Manufacturing

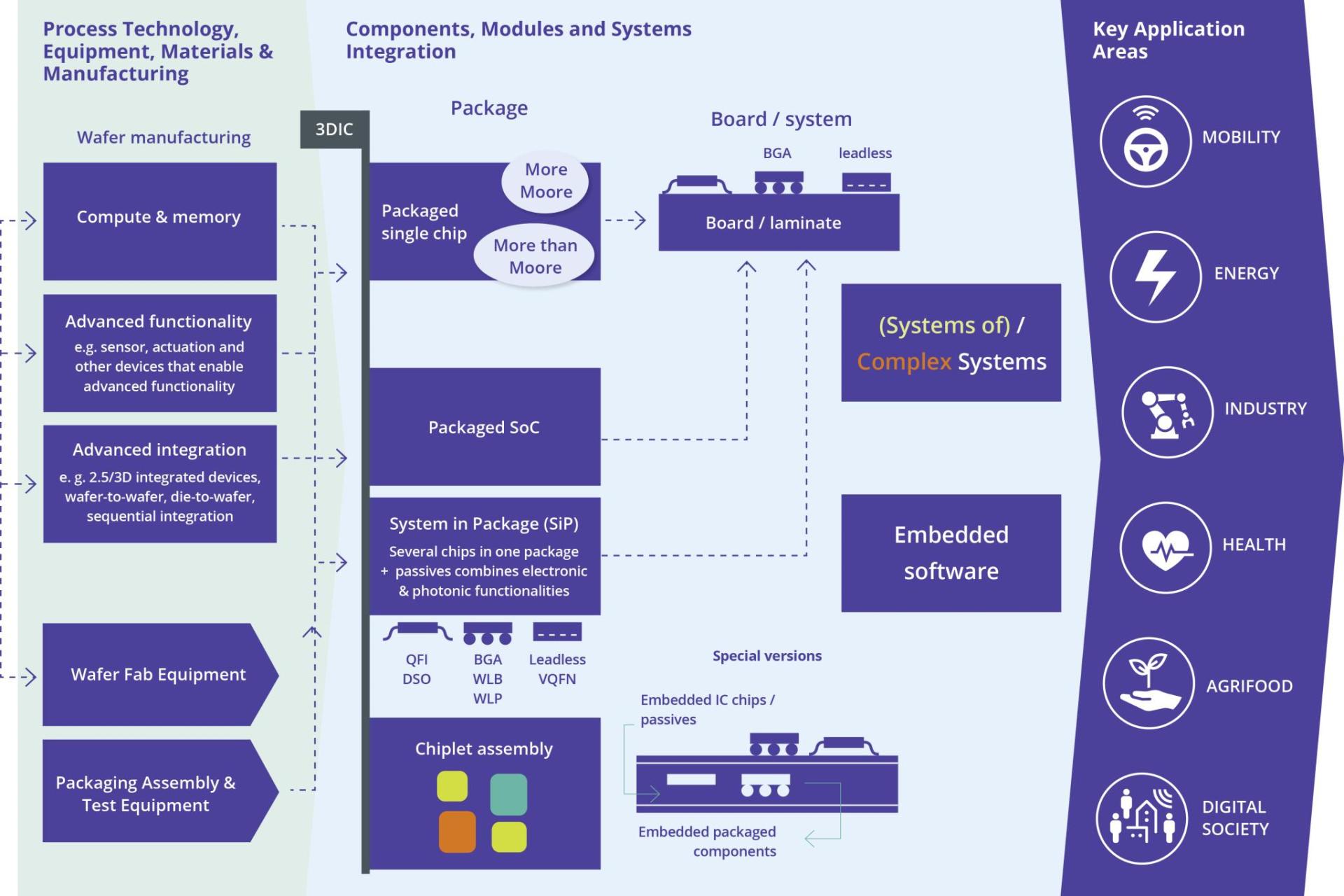

Semiconductor process technology, equipment, materials and manufacturing form the foundation of the ECS value chain producing the chip and packaged chip-level building blocks for all digital applications.

Nano- and microelectronics are key to achieving digital sovereignty in Europe, and they offer a range of solutions for a green and sustainable society. If Europe wants to control the development of a digital future fitted to its citizens and their requirements, as well as its social, economic, industrial and environmental goals, it needs continuous innovation in the field of semiconductor technology.

The key scope of this section is to cover all process technologies, equipment and materials’ research and innovation to enable semiconductor IC manufacturing inside a cleanroom environment. This includes:

-

New materials and engineered substrates to improve IC performance,

-

Process technologies, equipment and manufacturing technology to advance integrated circuit (IC) functionality and/or systems on chips,

-

Wafer level integration addressing a technology of packaging a die while it is still on the undiced wafer or bonded/attached to a wafer (D2W). Protective layers and electrical connections are added to the substrate before dicing.

Clearly, the scope of this section as indicated in figure 1.1.1 below involves synergies with other sections in this ECS-SRIA. First and foremost, the section links with Components, Modules and System Integration in Chapter 1.2. In addition, this section also links with Embedded Software and System of Systems (SoS) to allow for an integral system technology co-optimisation approach to deliver application-driven solutions. More details about the synergies with other sections are described in Sub-section 1.1.6.![]()

The main breakthrough enabled by the technological advances discussed in this section concerns the reduction of energy consumption in the various electronic components without any decrease in their performance.

In 2022, the globally consumed power of data centres alone was 240-340 TWh1, which represents between 1-1.3% of global final electricity demand. This excludes energy used for cryptocurrency mining, which was estimated to be around 110 TWh in 2022, accounting for 0.4% of annual global electricity demand. Investing in more efficient IT hardware including microchips will provide the means to flatten this curve whilst data centre workloads are expected to dramatically increase2.

Reducing the energy consumption of electronic components is essential for improving the autonomy of electric and hybrid vehicles, the lifetime of battery-powered sensors (for health monitoring, preserving natural resources such as water through more efficient irrigation, etc.), as well as for the development of autonomous sensors with energy harvesters and energy storage.

Since moving data from the logic cores to the adjacent memories is the main contributor to the energy consumption of logic devices (microprocessing units (MPUs), microcontroller units (MCUs), etc), their conventional von Neumann architecture must be drastically changed in close co-optimisation with other technology innovations. Near-memory or in-memory computing and neuromorphic computing are new architecture paradigms that strongly reduce the movement of data, and accordingly allow decreased overall energy consumption. Specific low- power transistors, memory and 3D-integration technologies need to be developed to ensure close coupling between computer and memory blocks.

The adoption of wide bandgap materials such as GaN and SiC is crucial for allowing higher operating temperatures and reducing the switching losses in power electronics for a broad range of power systems, such as smart phone/tablet chargers, industrial power supplies, power supplies for servers, etc., and - very important -, electric vehicles, thus increasing their range. GaN/SiC is also important for increasing the power efficiency of 5G RF base stations. In addition, GaN/Si and GaN/SOI can induce the same effect in RF front-end modules when combined with high thermally conductive materials.

The exponential increase in internet traffic (with a CAGR at 24% from 2021 to 20263) sets demanding requirements on data communication technologies. New architectures and technologies will be also essential for the future development of 6G communications, for improving the bandwidth and data transmission rate, while exhibiting lower latency and lower power consumption.

Optical interconnects enable higher bandwidth- distance products, higher bandwidth density, lower electromagnetic interference, and potentially lower power consumption than electrical interconnects. They are being deployed at increasingly shorter distances – for example, within and between data centres. In the longer term, chip-to-chip and even intra-chip communication may be performed with CMOS-compatible photonics. Beyond these applications, emerging precision applications – including atomic clocks, precision metrology, and transformative applications such as quantum communications and information processing – will also benefit from photonic capabilities integrated with electronics. These photonic capabilities range from silicon and heterogeneous III/V (membrane) photonics, to potentially disruptive technologies such as nanophotonics, and 2-D materials or graphene-based photonics. Additionally, developments in novel computing paradigms such as photonic and quantum computing threaten to make current security protocols insecure and will require the development of novel, future-proof cryptographic methods.

Other breakthroughs will concern adding intelligence close to the sensors (Intelligence at the edge) and/or to the data sources (IoT), and to integrate the components in a form factor that perfectly suits their applications. The initial generation of “Internet-of-Things” management was cloud-centric, where sensor data were collected from the periphery (or “edge”), then processed and analysed at the enterprise or platform tier. However, in that case, a tremendous amount of data needs to flow to the cloud and back, and a large amount of data processing power is required to structure and analyse it. In such a cloud-focused solution, latency and privacy concerns are often worrisome, or even prohibitive.

The term “embedded AI” or “edge AI” denotes how AI algorithms can be processed locally on a hardware device (e.g. a sensor) close to where the data is generated, and an action may then be required. A device using edge AI can process data it has collected and subsequently take decisions independently, without connecting to a central processing unit (CPU). Where initially local decisions will be supported by inference actions, there will be an evolution to training on the edge devices. Edge AI extends embedded computing, and contributes to economically effective solutions for the societal challenges we are facing in terms of: ![]()

-

Reducing the energy consumption of the data infrastructure by transmitting only relevant data or pre-treated information (countering the unsustainable explosion of the energy demand by data centres and by telecommunication systems requiring higher bandwidths).

-

Protecting personal data (GDPR compliance) by local processing and anonymisation of transmitted information.

-

Increasing security and resilience due to a reduced reliance on telecommunication links as a result of local decision-making.

-

Reducing latency by reducing the quantity of data needed to be transferred to and from a cloud, which is particularly important for automotive, digital society (real-time control of power distribution, for instance) and manufacturing applications, as well as some health applications.

Rethinking human activities to take advantage of the innovation opportunities offered by hyper-connectivity, AI solutions and new kinds of sensors based on miniaturised technologies will create numerous benefits for every new market, ranging from connected cars and digital health to smart home and smart living, and factories of the future. This should include lessons learned from the COVID-19 pandemic like the sudden increase in remote-working.

Sensors and biosensors will be an extensively studied discipline since their rapid, low-cost and highly sensitive features contribute to tremendous advances in many domains. Visible light, IR or multispectral imagers, lidar, radar and ultrasonic sensors, in combination with high-precision inertial sensors, will be essential for the deployment of advanced driver assistance systems (ADAS), augmented reality devices, and industrial automation for instance. Advancements in chemical-sensing technologies also open the door for multiple new markets. Gas sensors are increasingly integrated into IoT ecosystems to monitor air quality indoors and outdoors – for instance, wearable devices, smart city projects, sensor networks for pollution mapping, smart home electronics and automotive technology. Another key trend to utilise advanced gas-sensing technology is breath analysis, which aims at non-invasive diagnostics via detecting biomarkers from exhaled breath. Furthermore, pressure sensors in human and robot assisted minimally invasive surgery catheters are required to give haptic feedback to the surgeon. Miniaturized ultrasonic sensors open possibilities for minimally invasive medical imaging. However, to access the brain and smaller arteries in the body further miniaturization is required, posing a challenge for current pressure sensor technology.

R&D on highly selective biosensors will contribute to advances in next-generation healthcare, including personalised medicine and the ultrasensitive point-of-care detection of markers for diseases.

Next-generation electronic products are pushing the semiconductor industry to integrate more ultra-thin and flexible ICs. The combination of flexibility and processing capability is very desirable since it reduces weight and enables new form factors, while maintaining desirable functionality such as data logging and RF connectivity. Ultra-thin and flexible ICs enable more efficient and cost-effective solutions that will affect many applications, such as wireless communications, wearable electronics, implantable biomedical devices and the IoT.

The field of quantum sensing is rapidly expanding because quantum phenomena are extremely sensitive to their environment and thus can be used to measure physical properties with unprecedented precision. Quantum sensing refers to the process of employing an individual or an ensemble of quantum systems, often a quantum coherence and/or a quantum entanglement, to measure a physical quantity – ideally with improved accuracy, stability, sensitivity, sensitivity, precision, or spatial resolution compared to conventional measurements.

Quantum sensing usually describes one of the following:

-

Use of a quantum object to measure a physical quantity (classical or quantum). The quantum object is characterized by quantized discrete and resolvable energy levels. Specific examples include electronic, magnetic or vibrational states of superconducting or spin qubits, cold atoms, trapped ions, or photons.

-

Use of quantum coherence (i.e., wavelike spatial or temporal superposition of states) to measure a physical quantity.

-

Use of quantum entanglement to improve the sensitivity or precision of a measurement, beyond what is possible classically.

There are two generations of quantum sensors. The first, which includes devices such as microwave atomic clocks and superconducting quantum interference devices (SQUIDs), has been available for decades. The second generation, which includes atomic clocks, gravity sensors, magnetometers, gravimeters, gyroscopes, nitrogen-vacancy (NV) sensors, and other innovations, is just emerging. Second-generation quantum sensor applications may enable various domains:

-

Biomedical imaging: neural sensing and heart imaging.

-

Spectroscopy: imaging of molecular structure such as proteins.

-

Communications: Signal receiving and amplification for radar communication; calibrating electrical standards to support 5G/6G.

-

Navigation: Providing high-accuracy GPS; assisting with navigation inside buildings and underground.

-

Environmental monitoring: Predicting volcanic disruption and measuring CO2 emissions.

-

Infrastructure monitoring: Monitoring mechanical stability and detecting leaks.

-

Geographical surveying: Assisting with the location of oil and gas.

: Advanced computing, in-memory, neuromorphic, photonic and quantum computing concepts. Materials and substrates, process modules and integration technology for novel devices and circuits for advanced computing, memory and in-memory computing concepts based on nano-electronic, photonic, quantum or other technologies.

-

Major Challenge 1:Advanced computing, in-memory, neuromorphic, photonic and quantum computing concepts.

Materials and substrates, process modules and integration technology for novel devices and circuits for advanced computing, memory and in-memory computing concepts based on nano-electronic, photonic, quantum or other technologies.

-

Major Challenge 2: Novel sensor, actuation and other devices that enable advanced functionality.

Materials and substrates, process modules and wafer level integration technology for novel devices and circuits that enable advanced functionality: sensing including quantum sensing, actuating, power conversion, connectivity, etc.

-

Major Challenge 3:Advanced integration solutions.

Advanced integration including 2.5/3D integrated devices at wafer level, wafer-to-wafer (W2W) or material on wafer (sequential integration) or dies bonded/attached to a wafer (D2W), etc.

-

Major Challenge 4: Advanced wafer fab equipment and manufacturing solutions.

Equipment and manufacturing technologies for processing wafers in fabs from leading edge nodes to differentiated technologies and for advanced functionality devices, including new materials or unconventional geometry and heterogeneous integration technology options.

-

Major Challenge 5: Advanced packaging, assembly & test equipment solutions.

Equipment solutions to enable assembly and testing of a wide range of IC’s from logic and memory to advanced 2.5/3D integrated devices.

-

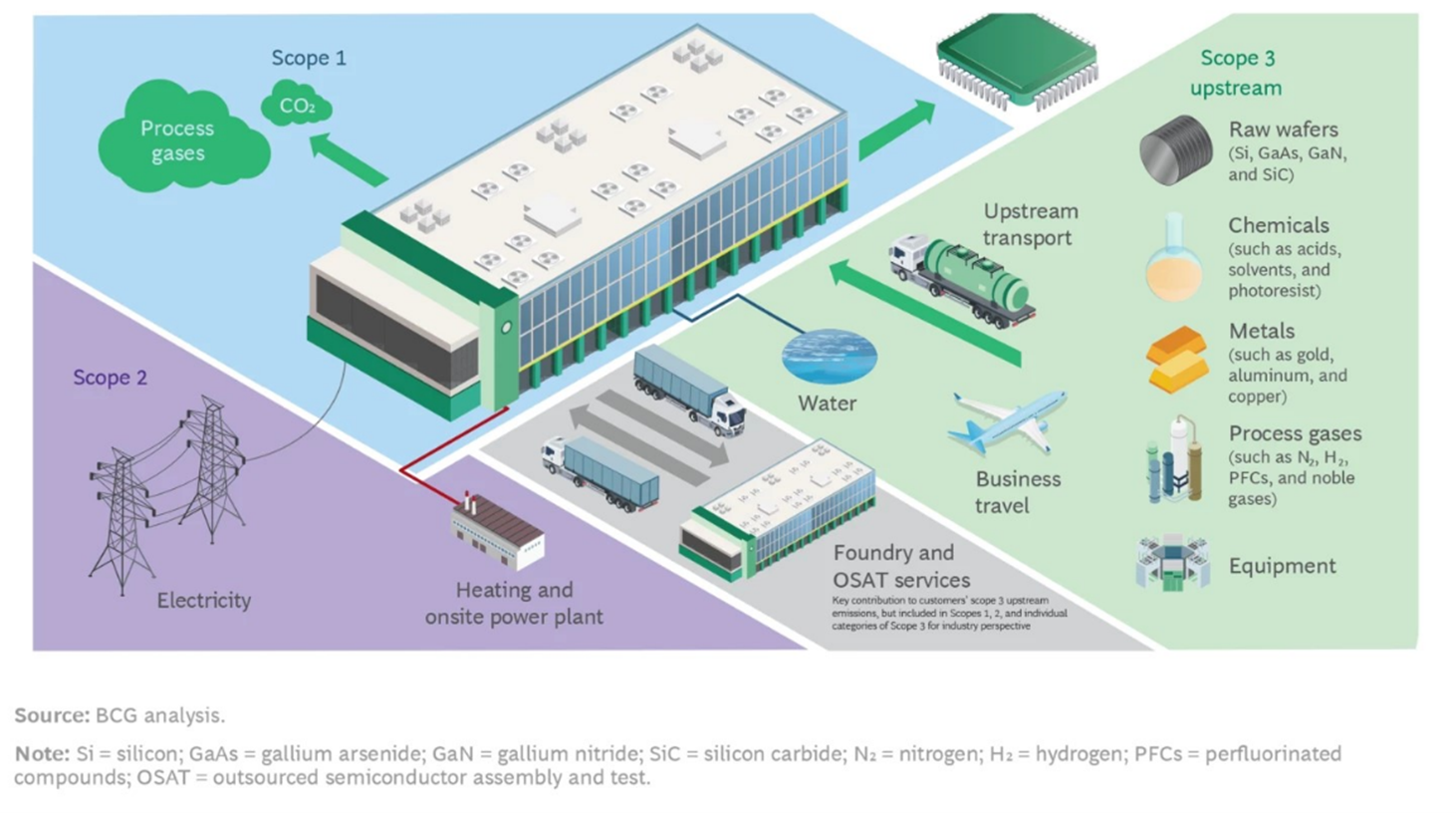

Major Challenge 6: Sustainable semiconductor manufacturing

Solutions to reduce Greenhouse gas emission, water & gas consumption and use of hazardous materials.

1.1.5.1 Major Challenge 1: Advanced computing, in-memory, neuromorphic, photonic and quantum computing concepts.

Semiconductor process technology and integration actions will focus on the introduction of new materials and substrates, process modules and integration technology, in close collaboration with the equipment, materials, modelling/simulation and embedded software communities, to allow for the necessary diversity in computing infrastructure. The applications range from high-performance cloud computing in servers for AI, ML and Gen AI data processing, edge computing/AI, and ultra-low power data processing at the IoT node level up to the highest possible performance. In order to lower the energy consumption of data transmission and processing, new currently investigated computing approaches such as in-memory and neuromorphic computing, or quantum computing (to solve classically unsolvable problems), the development of new materials, process modules and their integration in computing systems will be compulsory.

The obvious solution for transistors with increased electrical performances is the use of fully depleted devices. The industry has adopted three integration methods: FDSOI CMOS, FinFET and GAA-style CMOS devices. In chip design it is now embraced that these transistor integration methods enable complementary roles depending on the level of system requirements, ie. cloud-based services, edge computing or extreme-edge device functionality.

FDSOI is a 2D technology based on a thin buried oxide (BOX) layer under the CMOS channel. FDSOI exhibits several advantages, such as reducing the leakage current at standby mode and its higher tolerance against soft errors compared to traditional structures. FDSOI is perfectly suited for ultra-low-power IoT automotive, edge AI and 5/6G SoCs. The leading companies currently produce 18 nm and 22nm FDSOI-based chips. The pilot line on FDSOI will develop 10 and 7nm FDSOI technology nodes to allow a further reduction in energy consumption, while increasing its information processing performances thanks to the integration of embedded non-volatile memories, RF modules and 3D-integration options.

The 3D based FinFET and GAA devices provide high current drive, and hence higher speed, low leakage and, most importantly, less wafer area per transistor than the classic 2D metal–oxide–semiconductor field effect transistor (MOSFET) technology. These new devices are designed and processed to deliver better performance for applications in high- growth markets such as hyper-scale data centres, AI and ML, autonomous vehicles and power-efficient SoCs for the most demanding computer applications. The international industry value chain is pushing production beyond the 2 nm node by moving towards more 3D-stacked FET architectures, and requires solutions in materials and process integration challenges (High-NA EUV, 3D-integration for instance) to realise these novel devices.

Scaling further has recently been demonstrated being possible via the introduction of CFET (complementary FET) or 3D-stacked FET devices. A future sub-2nm advanced System-on-Chip pilot line will enable bringing R&D of this technology to higher maturity, including design enablement that will offer access to the European manufacturing and design Industry. This allows SME’s and start-ups to be competitive and strengthen EU’s position in the value chain, increasing the resilience and maintain relevance in the world race of addressing the ever-increasing user needs and societal challenges.

A clear differentiation between logic, memory and process information in conventional von Neumann computing schemes necessitates the frequent movement of data between the memory and processor. Thus, much of the execution time and energy consumption is spent in the movement of data, a barrier referred to as the “von Neumann bottleneck”, or “memory wall”. This obstacle has been greatly exacerbated since the advent of data-intensive computing applications, such as ML and Gen-AI. Near-memory and in-memory computing are new paradigms, wherein the computing system is redesigned to process data at its storage – in the memory – thereby minimising the expensive movement of data.

Near-memory computing involves adding or integrating logic (e.g. accelerators, very small cores, reconfigurable logic) close to or inside the memory. Logic cores are usually placed inside the logic layer of 3D-stacked memories or at the memory controller.

Silicon and organic interposers allow separate logic chips to be placed in the same die package as a 3D-stacked memory while still taking advantage of the through-silicon via (TSV) bandwidth. Some foundries (Intel, Samsung, TSMC, etc.) offer this kind of heterogeneous integration.

Recent advances in heterogeneous integration technology focus on integrating Si-bridges to connect dies together over very short distances along the die perimeter (e.g. Intel EMIB technology, TSMC implementation of SoIC and “CoWOS” technology).

These heterogeneous integration technologies (Interposers, bridges, chiplets) are often referred to as 2.5D as they still place active die next to each other in a 2D plane. Through 3D integration technology stack active devices are placed vertically on top of each other. This is commonly done in the field of CMOS image sensors and HBM (High Bandwidth Memory) DRAM stacks. These 3D integration technologies use TSV technology in the active die, in combination with high-density die-to-wafer or wafer-to-wafer interconnect technologies. This greatly increases the number of functional interconnects per die area on the functional chips. 3D-Interconnect pitches below 5 µm and even down to 400 nm have already been demonstrated.

An even denser 3D interconnect technology could be achieved by so-called “monolithic” 3D integration, a technique using sequential manufacturing of multiple layers of active devices and high density (Back-end of line) interconnect layers. Such monolithic integration is not currently available in foundries.

The amount of data processed in the cloud, the development of Internet-of-Things (IoT) applications, and growing data privacy concerns force the transition from cloud-based to edge-based processing. Limited energy and computational resources on edge push the transition from traditional von Neumann architectures to In-memory Computing (IMC), especially for machine learning and neural network applications. IMC also uses the intrinsic properties and operational principles of the memory cells and cell arrays, by inducing interactions between cells such that they can perform computations themselves. IMC aims to improve the energy efficiency of artificial/deep neural networks (ANN/DNN) hardware realizations by computing weighted-sum tasks in the memory arrays, for instance.

In an ANN chip, the neuron/synapse states are encoded as digital bits, clock cycles or voltage levels, while in a spiking neural network (SNN) chip, information is encoded into spike timing, to really mimic the biological brain operations. SNN hardware realizations are engineered to seek ultra-low power consumption and run at relatively low frequencies to emulate realistic biological behaviours, referred to as neuromorphic computing.

Due to the increasing need for large memory systems by modern applications (big data analytics, AI, etc.), dynamic random access memory (DRAM) and Flash memory scaling is being pushed to its practical limits. It is becoming more difficult to increase the density, reduce the latency and decrease the energy consumption of conventional DRAM and Flash memory architectures. 2D-NAND became monolithically integrated 3D-NAND, found the 3rd dimension for scaling, and DRAM currently follows the same path. This will seek innovation in DRAM select transistor channel material (ALD MX2, ALD Oxide Semiconductor etc.), capacitor dielectric, new cell architecture, new process steps etc. Alternative approaches are also being developed to overcome these barriers for implementing near- or in-memory and neuromorphic computing.

The first key approach consists of stacking multiple layers of memories (DRAM, Flash). With current manufacturing process technologies, thousands of TSVs can be placed within a single 3D-stacked memory chip. The TSV provide much greater internal memory bandwidth than the narrow memory channel. 3D-stacked DRAM and Flash are also commercially available.

The second major innovation is the use of emerging non-volatile memory (NVM) as parts of the main memory subsystem, and as embedded memories. New memory devices and technologies that are currently being investigated can both store data at high densities, lower costs, and present other benefits that will help computation with new in-memory computing paradigms: fast access time, long data retention, multilevel to analog ability and/or high endurance. The main emerging NVM technologies to allow in-memory computing architectures and embedded memories are: (i) phase-change memory (PCM), Threshold Change memory (TCM) ; (ii) magnetic RAM or spin-transfer or spin-orbit torque, or voltage-controlled magnetic anisotropy magnetic RAM (MRAM, STT-MRAM, SOT-MRAM, VCMA- MRAM); (iii) metal-oxide resistive RAM (RRAM or ReRAM) and conductive-bridge RAM (CBRAM) or memristors; (iv) ferroelectric FET (FeFET), RAM (FeRAM) and tunnel junctions (FTJ); (v) Electrochemical RAM (ECRAM) and (vi) Oxide Semiconductor (OSC) channel gain cell (2TnC, n=0 or 1). All these NVM types are expected to provide memory access latencies and energy usage that are competitive with - or close enough to - DRAM, while potentially enabling much larger non-volatility in main memory, and enabling new functionalities for computing systems outside Von Neuman architectures.

Thanks to its optimal compatibility to CMOS technology, Silicon Photonics is becoming a key material platform enabling technology for high-speed connectivity in data centres. In the near future, Photonic Integrated Circuits (PIC) can also bring significant changes to high-performance computers and unlocking the full potential of AI by resolving the transmission limits of electronics.

Photonic processors, that compute with photons instead of electrons, display some extraordinary properties, such as an ultra-wide communication bandwidth, ultra-high processing frequency, and ultra-low energy consumption. Additional dimensions division multiplexing of light field such as wavelength and spatial mode enable multithread processing with almost no extra computing overhead, leading to a significant acceleration against traditional electronic computers.

By combining the high bandwidth and parallelism of photonic devices, photonic neural networks (PNNs) have the potential to be orders of magnitude faster than state-of-the-art electronic processors while consuming less energy per computation. PNNs aim to leverage high-speed optical devices to mimic essential computing primitives (neurons and synapses) and connect them into a neural network (ANN/SNN) with highly parallel and dense optical interconnects.

The goal of neuromorphic photonic processors is not to replace conventional computers, but to enable applications that are unreachable at present by conventional computing technology in terms of low latency, high bandwidth and low energies.

Photonic processors have light sources, passive and active devices. Nowadays, more than 10 companies produce PICs worldwide, mainly based on SOI wafers. However, there is no commercial fabrication platform that can simultaneously offer devices for light generation, optical amplification, wavelength multiplexing, photo-detection, and transistors on a single die. State-of-the-art devices in each of these categories use different photonic materials (SiN, Ge, InP, GaAs, 2D materials, etc) with incongruous fabrication processes (SOI, CMOS, FinFETs).

Energy efficient and fast switching optical and electro-optical materials are needed for non-volatile photonic storage and weighing (synapses), as well as high-speed optical switching and routing, with low power consumption. Neural non-linearities are already possible on mainstream platforms using electro-optic transfer functions, but new materials promise significant performance opportunities. Phase change materials (PCMs), graphene and ITO-based modulators can also be utilized for implementing non-linearities (neurons).

On-chip optical gain and power will require co-integration with active III-V (InP or GaAs) lasers and semiconductor optical amplifiers. Current approaches involve either III-V to silicon wafer bonding (heterogeneous integration) or co-packaging with precise assembly (see also Chapter 1.2). Quantum dot lasers are another promising approach as they can be grown directly onto silicon, but fabrication reliability does not reach commercial standards today. Co-integrating CMOS controller chips with silicon photonics to provide electrical tuning control/stabilization, and robust packaging to prevent PIC temperature fluctuations, will be critical.

The past decade has seen an explosion in efforts to develop quantum computers that could revolutionize the fields of physics, medicine, biology, AI, finance and cryptography by exponentially speeding up certain computational domains. While such demonstrations certainly mark an essential technological milestone, tasks accomplished at such an unimaginable speed do not necessarily prelude the commercialization of quantum computers in the short term. To ensure the continued progression of quantum technologies over the next decade, advances in materials and fabrication processes are required for quantum computing hardware, following a path similar to the transistor technology scaling that enabled the evolution of digital computing.

Driven by market demand, on the one hand for advanced high-performance computing, AI/ML, and on the other hand for mobility, edge AI and IoT devices, the advanced Si technology roadmaps for both FinFET/GAA and FDSOI will need to be pushed further. To enable this, a wealth of explorations into novel low-thermal-budget-processing 2D materials, nanowires, nanosheets or nanoribbons and quantum dots needs to be combined with significant developments in advanced 3D integration schemes of materials and devices. In parallel, to overcome the von Neumann bottleneck, development of new computing paradigms such as neuromorphic, in-memory, photonic and quantum computing is essential. ![]()

New memory concepts will support the correct memory hierarchy in various applications. An example here is the opportunity to push new memory concepts (resistive RAM (RRAM), phase-change RAM (PCRAM), Thresholds Change RAM , STT- MRAM, FeFET, FeRAM, FTJ, Electro-Chemical RAM (EC-RAM)) to the demonstration level in the IoT infrastructure (from server, over edge to nodes). These alternative memories require the development of advanced novel materials (magnetic, phase-change, nanofilament, ferroelectric, electrochemical). A much closer collaboration between new material innovation, process, device integration, device teams and system architects, is indispensable in the future. New markets will require storage class memory to bridge the performance gap between DRAM and NAND Flash. Edge AI and IoT applications will require low-power embedded devices and cloud computing with more mass-storage space. The standard memory hierarchy is challenged. Indeed, learning algorithm requirement will dramatically increase the requirements on memories densities, access bandwidth and endurance on one hand, while new functionality - such as Multilevel to analog non-volatile memory cells - are required to allow efficient in memory computing approaches like ANN, from direct matrix vector multiplication to CNN or spike neural architectures. Simultaneously, advanced interconnect, System on Chip (SoC) integration issues will need to be addressed (cf. also Major challenges 2 and 3), with innovative solutions to reduce costs being required. The option to use advanced 3D and optical input/output (I/O) technological solutions, to circumvent limitations of traditional I/O architectures, are strengths to foster and build upon in Europe.

Furthermore, the downscaling of photonic components (light sources, modulators, photodetectors, optical phase shifters…) and their integration on CMOS platforms would lead to photonic neural networks (PNNs) for overcoming the current memory bottleneck. Such PNNs are expected to achieve orders of magnitude enhancement in energy efficiency and throughput compared to ANNs and SNNs. Hence, the intimate collaboration between the strong EU electronic and photonic communities would enhance the EU leadership in this domain.

One of the current major issues for most of the developed quantum technologies is their future scalability. For example, quantum computing error rates multiply as scale increases, and creating large numbers of qubits that are stable enough for long enough is extremely challenging. Collaboration between quantum “laboratories” and the EU electronic industry looks compulsory for strengthening the EU force in quantum computing.

To maintain the European competencies in advanced design for integrated circuits and systems, a close link with a strong effort in semiconductor process technology and integration has to be maintained. Issues such as the creation of standards for the IoT, reliability for safety or mission-critical applications, security and privacy requirements need close collaboration among all players to build leadership going forward in this coming generation of advanced and distributed computing infrastructure and diversified system performance.

Maintaining competence on advanced logic and memory technology in Europe is key to maintaining strategic autonomy and supporting societal benefits from the core technology base. Implementation of dedicated and sustainable pilot lines for specialised logic processes and devices supporting European critical applications is also a major objective, as is the exploration of new devices and architectures for low-power or harsh environment applications.

This challenge includes the following key focus areas:

Topic 1.1

-

Explorations of the scaled Si technology roadmaps of the 2 and 1 nm nodes including FinFET/Trigate and stacked gate-all-around horizontal or vertical nanowires, Forksheet-, complementary FET architectures, next generations FDSOI, 3D integration, and further device and pitch scaling, where parallel conduction paths (nanowires, nanosheets, nanoribbons, etc.) are brought even closer together. It includes novel device-interconnect technology such as - but not limited to - contact from wafer backside.

Topic 1.2

-

Exploration and implementation of materials beyond Si (SiGe, SiC, GaN, Ge, InGaAs, InP, functional oxides, 2D material heterostructures, CNT and nanowires).

-

Unconventional devices and materials, such as 2D and III-V materials, oxide-semiconductors, metamaterials, metasurfaces, nanowires, CNTs, nanosheets, nanoribbons, nanoparticles, quantum dots, spin effects, functional oxides, ferroelectric and magnetic, which are being investigated to overcome the limits of conventional CMOS logic and memories.

Topic 1.3

-

Novel device, circuit and systems concepts for optimum PPAC specifications, high-energy efficiency and novel paradigms such as for near/in-memory, neuromorphic, optical and quantum computing.

-

New Photonic integrated circuits (PIC) for a further improvement of optical I/Os for enabling compute, memory, and networking ASICs to communicate with dramatically increased bandwidth, lower latency and at a fraction of the power of existing electrical I/O solutions.

-

In a longer term, Photonic Neural Networks (PNNs) could bring the benefits of photonics over electronics (energy efficiency, low latency, higher bandwidth, parallelism…) to AI/ML.

Topic 1.4

-

Long-term challenges such as steep slope switches (tunnel FET, negative capacitance FET, nanoelectromechanical systems / NEMS), spin-based transistors, and alternative high- performance switches.

Topic 1.5

-

New embedded non-volatile memory (eNVM) technologies to enable local AI processing and storage of configuration data, which decrease data transmission volume, energy needs and allows for more efficient control of electric powertrains and batteries, along with many other applications in the IoT and secure devices domains.

1.1.5.2 Major Challenge 2: Novel devices and circuits that enable advanced functionality

Materials and substrates, process modules and wafer level integration technology for novel devices and circuits that enable advanced functionality: sensing - including quantum sensing, actuating, power conversion, connectivity, etc.

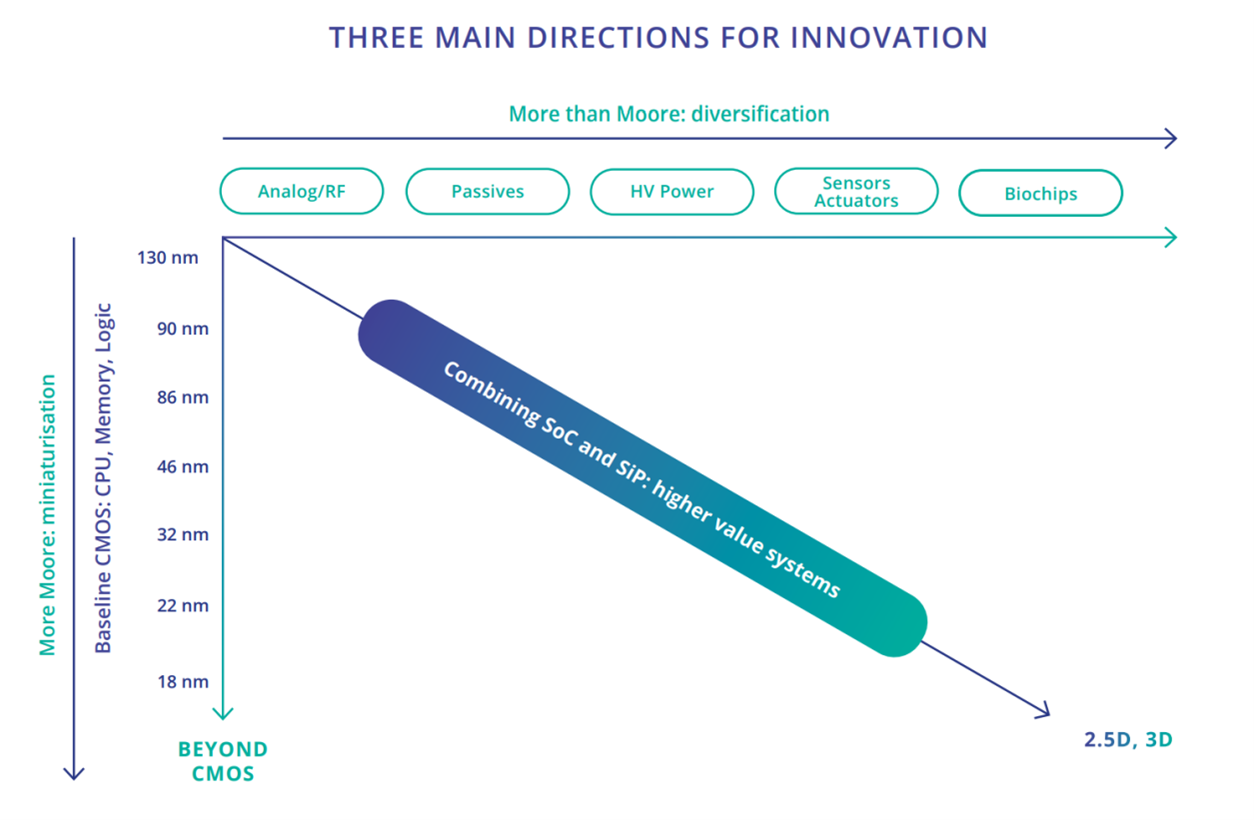

Besides the highly integrated chips necessary to overcome Major Challenge 1 on advanced computing, memory and in-memory computing concepts, many more devices are needed to achieve advanced functionalities – such as sensing and actuating, power management, and interfaces to other systems. This is what has also been named “More than Moore” for the past 20 years, and is an integral part of all systems, as well as one of the strengths of European microelectronics. Given the inherently diverse nature of this sector, the state of the art will be captured by providing a few snapshots of key technologies.

For IoT applications, logic and RF functions are combined, but not with the highest efficiency required by the ultra-long lifetime of unattended objects. Energy harvesting schemes, often based on photovoltaics, do exist, yet are not always able to provide the requested energy supplement of self-contained low-volume and low-cost sensor nodes.

Smart optical, mechanical and magnetic sensors are already able to provide a wealth of information for complex systems. Nevertheless, there are current limits to integrating various types of sensors monolithically. In the field of optical sensors, for instance, depth mapping requires complex scanning schemes using either mechanical systems or large volume and poorly integrated light sources. Devices based on rare or expensive materials, which are not compatible with standard CMOS technology, cover various useful zones of the electromagnetic spectrum. The same is true for chemical-sensing technologies, which are mostly based on metal oxides or other coated materials. While solutions for specific gases and applications are starting to emerge, sensitive and robust technologies using semiconductors still remain to be developed for a large number of applications and species, or to enhance the performance in concentration ranges, selectivity and stability. The situation is similar for many kinds of sensors and actuators. For instance, fine pitch displays are beginning to be possible, but will require new advances, both in high brightness / low variation sources and assembly methods.![]()

Technologies used for the next generation of quantum sensing include neutral atoms, trapped ions, spin qubits, superconducting devices, and photonics. Please note that in the previous sentence “quantum sensing” means sensing using individual quantum objects and their entanglement. They can be used to measure the magnetic field (B), the electric field (E), the rotation (θ), the acceleration (g), the time (t), the frequency (f), the temperature (T), the pressure (P), the force (F), the mass (m) and the voltage (V) (Table 1). Charged systems, like trapped ions, will be sensitive to electrical fields, while spin-based systems will mainly respond to magnetic fields. Some quantum sensors may respond to several physical parameters.

In the more conventional light sensing techniques, sensors are often based on the absorption of a given semiconductor species, which leads to a rather broad but limited energy range. Emerging techniques to tailor the wavelength range by either confinement of the sensing element (“quantum dots”) or the combination of different materials in the same stack. The question of wavelength selection, in case a further wavelength selectivity is needed - for instance to address both the visible and near infrared bands - is usually addressed by stacking different sensing elements and optical filters of various principles.

In power technologies, recent years have seen the emergence of wide bandgap materials able to reduce the losses of power conversion, namely SiC and GaN, or other wide bandgap technologies. These technologies are making quick inroads as one of the cornerstones for the energy transition, and are becoming dominant in some sectors, like high-power electric motors... However, they are still nascent, and the challenge is to develop low-cost (involving larger diameter, good quality and less-expensive substrates) and robust technologies. Today, SiC is produced mainly on 150 mm substrates, while some GaN devices are produced on silicon substrates, but the technology and epitaxy techniques will still need further refinement (and even breakthroughs). Moreover, the development of disruptive substrate technologies as well as layer transfer will be key steps toward a cost-effective, high-performance solution linked with transition to 200 mm, then from 200 mm to 300 mm substrates where possible and where volumes justify it. This is essential for future integrated logic and power management functions using technologies combining logic and power transistors. Besides research on wide bandgap materials, the Si-based insulated-gate bipolar transistor (IGBT) technologies have further innovation potential in the area of cost-sensitive applications. Challenges are in the domain of high-power and high-voltage electronics with high junction temperatures processed towards larger diameter substrates – leading to increased power densities and lower costs to support the transformation in the energy systems with Si-based power semiconductors. In some cases, the power dissipation of the devices - which remains high despite their better efficiency - is a real challenge and needs to be addressed both at device and wafer level and at the packaging level (see also Chapter 1.2).

For RF and communication technologies, recent advances in integrating RF technologies on low-loss substrates such as SOI have allowed the integration of switches as well as amplifiers on the same silicon substrates. This concept is in production in Europe on 200 mm and 300 mm wafer substrates. Further advances are on the way on both substrate diameters, which will allow the integration of more functions and address the requirements of complex 5G systems below and beyond 6 GHz, up to the mm waveband. Synthetic antennae systems for radar or communications are emerging thanks to highly integrated RF technologies, including BiCMOS, but are often limited by power consumption and costs. For example, BiCMOS brings advantages over some III-V technologies for some applications, leveraging the capability to integrate digital functions. For sure, it cannot compete with GaN when very high power is requested, but GaN can neither compete with BiCMOS for the products requiring mixed-signal functions. New, RF technologies delivering high output power and efficiency like RF GaN (GaN-SiC as well as GaN-Si) and other III-V based materials - such as InP - could overcome these limitations. Those technologies have to be considered either stand-alone or in combination with either RFCMOS or BiCMOS using heterogenous integration. In the field of communications, the integration of photonics technologies with electronics is gaining commercial ground. Further advances in efficient source integration, and modulation and power efficiency, are still needed to use them more widely. New advances in fine photon handling can also open the way to innovative sensing techniques, either by using light interaction with the signal to be measured outside the PIC and sensing the effect of this interaction within the PIC, or by using the PIC as an actuator, for instance implementing optical (phased array) antennae.

In optical communications, the intrinsic capability of light waves to transmit signals with low latency and power dissipation, at ultra-high data rates, can be scaled from long-haul infrastructures to intra-datacenter optical links, down to chip-to-chip photonic interconnects. However, bulk silicon cannot meet the necessary requirements of these integrated optics applications which can be addressed with silicon-on-insulator (SOI) technology. SOI photonics, which is part of Silicon Photonics, is one route to enable the development of novel lidar systems as well as support advancements in quantum technologies. By leveraging mature semiconductor manufacturing methods, engineered wafers that incorporate SOI technology offer a powerful approach toward broader adoption of advanced chip-scale integrated optics. In addition to substrate progress a host of innovations will be necessary - and are expected - to boost the (Silicon) Photonics Integrated Circuits (PIC). Among those are new generations of active devices including the heterogeneous integration of active devices (sources, modulators) or passive components and detectors (mainly for sensing), for example for wavelengths outside the communication frequencies. They involve new materials and integration techniques.

In “traditional” polyimide (PI)-based flexible electronics, the continuing trend is towards more complex designs and large-area processing, especially in displays and sensor arrays. Since the achievement of high-performing flexible electronics by monolithic approaches is limited, hybrid approaches are used when conventional electronics (such as thinned chips) is assembled on flexible electronic substrates. For more complex devices, the reliability and performance of organic materials or mechanical and processing properties of inorganic materials are still a focus of research activities in addition to adapted and optimised assembly techniques. In general, current R&D activities indicate that technical spots can be identified where a merging of novel flexible devices and adapted Si electronics create progress beyond the state of the art.

Depending on the application, the advantages of More-than-Moore (or SoC) technology are size, performance, cost, reliability, security and simpler logistics. Therefore, this approach is a key enabler for the European industry. To maintain and strengthen Europe’s position, it is necessary to improve existing technologies, and to seamlessly integrate emerging technologies in a reliable and competitive way. All application domains addressed by the ECS SRIA will benefit from components with very diverse functionalities.

Specific process technology platforms may be required, as in the case of biomedical devices for minimally invasive healthcare or point-of-care diagnosis, or mission-critical devices in automotive, avionics and space. Semiconductor process and integration technologies for enabling heterogeneous SoC functionality will focus on the introduction of advanced functional (nano-)materials providing additional functionalities and advanced device concepts.

Innovations for these domains require the exploration and functional integration, preferably in CMOS- compatible processing, of novel materials. A non-exhaustive materials list includes wide bandgap materials, III-V semiconductor compounds, 2D materials (e.g. graphene, MoS2 and other transition metal dichalcogenides), 1D (e.g. nanowires, carbon nanotubes) and 0D (e.g. nanoparticles, quantum dots) materials, metal oxides, organic semiconductors, ferro- and piezoelectric, thermoelectric and magnetic thin films materials, materials with specific properties (for optics: dielectrics, bi-refringent, phase change materials which can also be used for conductivity change properties, for electromagnetic properties: low permittivity, etc..), metamaterials and metasurfaces. Obviously, safety and environmental aspects should also be taken into consideration.

The driver for SoC integration is always a clear demand from the application domain. To maintain and push forward Europe’s position, the focus should be on emerging technologies as they are introduced, as well as new developments in the equipment and materials industry, in which Europe has a leading position. Furthermore, the early generation of models and their initial validation for benchmarking and intellectual property (IP) generation are required to reinforce position of Europe in specific design concepts and architecture, especially when used in combination with re-use IP and third-party IP blocks to secure fast time to market.

This will involve the implementation of pilot lines for integrated application-defined sensors, novel IoT solutions, complex sensor systems and new (bio)medical devices, new RF and mm-wave device options (including radar and sensing), much more efficient power management, higher integration of passive devices, photonics circuits and options, novel and more efficient displays and electronics, this list being non exhaustive. Key will be the initiation of process technology platforms for the exploration and exploitation of advanced functionalities through integration of novel reliable materials.

The exploration and implementation of materials beyond Si will require strategic collaborative EU projects for European industry to become more independent, and will result in the development of an EU-based supply chain for wide-bandgap materials, for example, including a move towards larger substrate sizes of 200 and 300 mm (i.e. SiC and GaN, and also InP which provides a further challenge to GaN in that it cannot be grown on Si).

More specifically, the following challenges are identified (this is a non-exhaustive list).

Topic 2.1: Application-specific logic: as explicitly treated in sub-section 1.1.4.3, heterogeneous SoC integration can require specific solutions for logic to be integrated with More-than-Moore technologies such as the following:

-

Logic integration with RF, optical or sensor technologies.

-

Integration of lasers and detectors within silicon photonics platform.

Topic 2.2: Advanced sensor and actuators technologies:

-

Mechanical sensors and actuators (e.g. acceleration, gyroscopes, microphones and microspeakers).

-

Chemical sensor devices such as selective gas-sensing components for environmental monitoring or smart medicine and smart health (e.g. CO, CO2, NOx, O3, toluene, VOCs, acetone, H2S, etc…).

-

Physical sensors (magnetic, optical, RF).

-

Multispectral or highly sensitive optical sensors.

-

Transmitter/receiver technologies for applications such as lidar and active phased array imaging.

-

Biomedical and biochemical sensors.

-

New, more efficient displays, in particular micro displays.

-

environmental protection technologies for audio MEMS and integrated technologies for enhanced robustness against outer environment for MEMS based audio devices.

Topic 2.3: Advanced power electronics technologies (Si-based, BCD, SiC, GaN, Ga2O3, AlN etc.) to enhance the efficiency of motors, energy storage, lighting systems, etc. More specifically:

-

Higher power density and frequency, wide-bandgap materials for high temperature electronics, new CMOS/IGBT processes, integrated logic, uni- and bipolar; high voltage classes, lateral to vertical architectures.

-

Materials for energy harvesting (e.g. perovskite solar cells, piezoelectric ceramics and thin films) and storage (e.g. perovskites, ferroelectrics and relaxors), micro-batteries, supercapacitors and wireless power transfer.

-

Power devices and modules for highly demanding automotive, industrial and energy infrastructure applications.

-

Substrates towards larger diameters to serve future greater demand for cost-sensitive power solutions.

Topic 2.4: Quantum sensor technologies:

-

Atomic vapor or cold atom (Bose-Einstein condensate) based sensors.

-

Trapped ion-based quantum sensors.

-

Solid state spinbased quantum sensors making use of Nitrogen-Vacancies or color centres as sensitive element.

-

Superconducting circuit sensors based on SQUIDS, flux qubits and charge qubits.

-

Sensors based on photon entanglement using nonlinear optical media.

Topic 2.5: Advanced RF and photonics communication technologies to interface between semiconductors components, subsystems and systems. These technologies should enable better and more energy-efficient control of emission and reception channels (for example, for 5G connectivity and 6G) via:

-

New energy-efficient RF and mm-wave integrated device options, including radar (building on e.g. SiGe/BiCMOS, FD SOI, CMOS, GaN or other III-V compounds, PIC).

-

Development and characterisation of new RF cryogenic electronics for Quantum Information Processing (QIP), as well as logic devices at quantum-enabling cryogenic temperatures, taking into account the available cooling power of refrigerators and interfacing requirements at different operation temperatures.

-

Energy-efficient computing and communication, including a focus on developing new technologies.

-

Bringing MOEMS and micro-optics, nanophotonics, optical interconnections, photonics-enabled device and system options into a CMOS-compatible manufacturing flow.

1.1.5.3 Major Challenge 3: Advanced integration solutions

Advanced integration including 2.5/3D integrated devices at wafer level, wafer-to-wafer (W2W) or material on wafer (sequential integration) or dies bonded/attached to a wafer (D2W), etc.

By splitting the chip into smaller functional physically separate parts, the overall system yield improves and system performance is enhanced. In addition, by using system-independent IP block design and verification, as well as common die-to-die interfaces (including IP re-use and use of third-party IP), a faster time to market can be achieved. One counterpart being that the design and testing strategy needs to be entirely revised in order not to lose the yield advantage, and that assembly costs (as collective as possible) and yields must also be mastered. This is the key overarching challenge of this approach.

Over the last few years, a huge variety of semiconductor products have emerged where several functions are added in one IC, enabled by advances in integration technology. This is the so-called System In Package (SiP) approach.

To maximise the benefits from ICs made of small geometry nodes, below 40 nm typically, and certainly as of 7 nm and less, there has already been a move to more advanced methods, to manage complexity in the most cost-effective way. These advanced integration methods involve technologies such as flip chip, but also - depending on the use cases - wafer-level packaging, fan-out wafer-level packages without substrate interposers and complex 3D structures with TSVs, micro-bumps and thin dice.

The functional diversification of technologies, where digital electronics meets areas such as analog, photonic and MEMS technologies, has been advanced through the assembly of heterogeneous elements. For example, in today’s power stages in automotive powertrain applications, power modules integrate several dice in parallel. Similarly, 5G networks are enabled by advanced RF functionality, often combining a photonic interface with in-package integrated logic and memory functionalities. Semiconductor materials encapsuled in packaging technology have already moved from being largely silicon-based or based on III-V compounds for photonic or high-power RF applications, to more advanced SiC and GaN compounds. On the part of the package, the industry has moved towards environmentally friendly lead (Pb) and halogen-free moulding compounds. For wire bonding, a similar move from aluminium and gold towards copper and silver wiring has been made. Furthermore, flip chip attach has made a transition to lead-free bumps (inside the package) and BGA using lead-free balls (at the interface between the package and the board) materials.

This challenge covers the integration of new chip technologies in advanced low parasitic packages, as well as chips of different functionalities resulting from the previous two challenges – e.g. CMOS logic, NVM, NEMS/ MEMS, RF, analogue, sensing, actuating, optical, power management, energy harvesting and storage – into a SiP.

Depending on the application and type of system, the key drivers and parameters to be improved can be the density of contacts, the parasitics, the integration of passives - including antennae -, the thermal dissipation, the optical quality, the number of dice to be integrated either horizontally or vertically, the ability to handle various environmental conditions, including extreme temperatures or resistance to chemicals, etc. ..It is becoming more and more clear to everyone that the overall performance of the system is dependent not only on the semiconductor technologies but also - and sometimes in equal part, or even predominantly - on the integration technology.

Advanced integration technologies are required for mm-wave applications (> 30 GHz), both GaN/Si RF and other high-electron-mobility-transistor (HEMT) devices, or dedicated MEMS and sensor devices (e.g. electro-optics for lidar without moving parts) and display technologies used in AR/VR. Depending on the application, heterogeneous integration technology can provide a better compromise between available functions, performance, cost and time to market.

System integration technologies are a key enabler for the European industry, including for instance the essential field of energy transition with power management devices, but also longer term evolutions, like the new field of cryogenic QIP, characterisation of logic devices at quantum-enabling cryogenic temperatures, and associated packaging challenges. To maintain and strengthen Europe’s position, it is necessary to improve existing technologies and develop emerging technologies, as well as to integrate both to advanced electronic systems in a competitive and reliable way. All application domains addressed by the ECS agenda will benefit from innovative integration technologies.

Moreover, component carriers also known as Integrated Circuit (IC) Substrates represent a big portion of the package cost (up to 50%), excluding the semiconductor component itself. This is particularly true for Flip Chip Ball Grid Array (FC-BGA) Substrates, which are essential component carriers in high-performance, high-interconnect density computing solutions. Due to the increase of functionality and driven by chiplets integration, FC-BGA substrates are facing many challenges, not only in terms of miniaturization, but they are also becoming central elements for thermal management in advanced computing systems.

Integration of the above functionalities in miniaturised packages and (sub)SiP require fundamental insights into application needs and system architecture. Process and characterisation technology to realise this integration is part of this third Major Challenge, and is essential for ensuring Europe’s prominent role in supplying novel solutions for the various existing and emerging application domains.

At the macro-scale level, a system consists of a collection of large functional blocks. These blocks have quite different performance requirements (analogue, high voltage, eNVM, advanced CMOS, fast static RAM (SRAM), multi-sensing capability, etc) and technology roadmaps. Therefore, for many applications it is of increasing interest to split the system into heterogeneous parts, each realised by optimum technologies at lower cost per function, and assembled with parts using high-density 3D interconnect processes. In other words, for each application or system the SoC / SiP trade-offs and partitioning have to be revisited in the light of the respective evolutions of base technologies.

It is clear that 3D integration in electronic systems can be realised at different levels of the interconnect hierarchy, each having a different vertical interconnect density. Different technologies are therefore required at different levels of this 3D hierarchy.

For the reasons above the Electronic Design Automation of 3D integration is to be much further explored and constitutes a very challenging domain as described in Chapter 2.3.

Research and development priorities are focused on innovative approaches, such as the following.

Topic 3.1: Advanced Si interconnect technologies:

-

Interconnect technologies that allow vertical as well as horizontal integration: this includes process technologies for vertical interconnects, such as TSV, through-encapsulant via (TEV), through-glass via technologies and microbumps, and copper/copper bonding, as well as process technologies for horizontal interconnects such as thin film technologies for redistribution on chips.

-

Implementation of advanced nanomaterials and metamaterials, including low-thermal-budget-processing 2D materials, nanowires, nanoparticles and quantum dots with scalable logic and memory device technologies.

-

New materials to maximize efficiency of the Package Thermal dissipation (Flip Chip Thermal Enhanced BGA) is required to deal with the very demanding computing applications in extreme conditions i.e. Automotive, space environment.

-

New materials like Al bumps from Electroplating could solve reliability issues and ensure advanced CMOS compatible integration.

-

Power electronic substrates will benefit from thick Al layers fabricated by novel electroplating technologies and other thermal redistribution techniques.

Topic 3.2: Specific sensing, actuation and display technologies.

-

Solutions for advanced optical functionalities on wafer, either for sensors (visible, NIR, infrared), for PIC, or for AR/VR, near-eye and head up displays, or any optical system.

-

Specific solutions for the signal conditioning of other sensors (mechanical, physical, chemical…)

-

Increasing functionality in IC Substrates for high efficiency power delivery including voltage regulator circuitry and integrated capacitances and other passives.

Topic 3.3: 3D integration technologies:

-

High-integration density and performance-driven 3D integration (power/speed). For this category, denser 3D integration technologies are required: from the chip I/O-pad level 3D-SIP, to finer grain partitioning of the 3D-SOC and the ultimate transistor-level 3D-IC (see Sub-section 2.3.1 for the 3D landscape).

-

Chip-package-board co-design. This will be of utmost importance for introducing innovative products efficiently with a short time to market (and which is closely linked to the work described in Section 2.2).

-

System integration partitioning: the choice of 3D interconnect level(s) has a significant impact on system design and the required 3D technology, resulting in a strong interaction need between system design and technology with a significant impact on electronic design automation (EDA) tools.

System requirements and semiconductor device technology (Major Challenges 1 and 2) will evolve at the same time, creating momentum for further interconnect pitch scaling for 3D integration technology platforms. Hence, the timelines of all four challenges of this section are strongly connected.

1.1.5.4 Major Challenge 4: Advanced wafer fab equipment solutions

This is about equipment and manufacturing technologies for processing wafers in fabs, from leading edge nodes to differentiated or mature technologies and for advanced functionality devices, including new materials or unconventional geometry and heterogeneous integration technology options.

The semiconductor equipment and manufacturing sector in Europe provides the global market with best- in-class equipment to enable the manufacturing of miniaturised electronic components. The European equipment industry, RTOs and small and medium-sized enterprises (SMEs) active in this sector have a long history of successful mechanical engineering, tailor-made machinery, optical equipment, metrology, inspection and testing equipment, and chemical processing tools. This history of success is prominent in several domains, foremost in lithography (in particular EUV) and metrology, but also in thermal processing, deposition, etching, cleaning and wafer handling.

At the forefront of semiconductor manufacturing equipment is the production of logic and high-performance memory, which are applied mainly in portable devices as well as advanced cloud computing and data storage facilities. The continuous increase of device density known as Moore’s law is being driven by an ability to create ever-smaller features on wafers. The technology leaps required to keep up with Moore’s law have already been achieved via additional roadmaps complementing ongoing 2D pattern size reductions. They are realised by combining various devices, materials, and 3D and system architecture aspects that required dedicated long-term investment in high-tech equipment solutions. Enabled by current deposition, lithography, etch, processing and metrology tools and their performance, the 3nm technology node is in production by market leaders, solutions for 2nm node are planned for 20254, and even Angstrom nodes5 are being explored.

For the production of miniaturised and reliable More-than-Moore electronic components and systems, such as sensors and sensor systems, MEMS, advanced imagers, power electronics devices, automotive electronics, embedded memory devices, mm-wave technologies, and advanced low-power RF technology, many equipment and manufacturing solutions have been implemented.

The ever-increasing demand for leading-edge logic and memory technology is driving the development of new equipment and material solutions for sub-2 nm node semiconductor technologies. Besides finding equipment solutions for further shrinking minimum feature sizes well below 1 nm, the alignment accuracy of successive layers, called “overlay” or in another definition type “Edge Placement Error”, needs to move towards Angstrom levels in a process technology roadmap that combines complex materials in 3D structures and architectures. At the same time, productivity demands on the equipment continue to increase to maintain reduced overall production costs. Process yield also continues to be a challenge with shrinking feature size and the increasing impact of defects and contamination.

In the realm of cutting-edge technology, the advent into new nodes necessitates the development of novel materials. These materials are either integrated into the structure to enhance electrical properties or utilized as sacrificial elements to facilitate the creation of intricate 3D shapes. The precision in material deposition is becoming increasingly critical, requiring meticulous control over where materials are applied, their thickness, and whether they are deposited on horizontal or vertical surfaces.

The semiconductor industry is driven by the dual goals of boosting productivity and slashing energy and water consumption. Wafer fabs are striving to process more wafers per hour without increasing power usage, achieved through enhanced equipment throughput, real-time optimization of production flows and streamlined processes. Despite variations in throughput across different equipment types—such as lithography’s DUV throughput at approximately 295 wafers per hour, whereas throughput in deposition might take up to a few minutes for single wafer processes—there is a universal push for higher throughput and yield, alongside refined process control to minimize additional steps and reduce defective wafers. This pursuit has led to the development of more sophisticated equipment in patterning, processing and metrology, with kWh/wafer serving as a pivotal metric for sustainable innovation.

The increasing technical complexity calls for more efficient design and production methods. At factory level, solutions based on advanced mathematics, statistics or AI should enable extension across current domains enabling a wider scale integration. Advanced data modelling and analysis techniques, combined with generative AI should rapidly enable smarter detection of deviations (whether its process or product quality, equipment or global production performance) together with faster reaction thanks to AI augmented troubleshooting and guided analysis.

The intricate nature of future semiconductor manufacturing equipment requires a substantial increase in skilled labor for design and realization. Without advancements in efficiency, the local labor market may fall short in providing the necessary expertise, potentially slowing down innovation and affecting profit margins. In this domain as well, generative AI can be instrumental in mining existing knowledge deposits to support transfer to new generations. New methods will have to be developed to ensure the efficiency of this transfer and the sustainability of European know-how. While the use of generative AI should also enable the integration of this knowledge into software assistants or copilots and eventually autonomous systems, techniques will have to be developed to ensure that the system will stay in (human) control.

Automation trends like Industry 4.0 and 5.0 are reshaping manufacturing, demanding greater data exchange and secure integration of design data into production processes. This evolution aligns with the Smart Industry roadmap.

Environmental considerations are also at the forefront, with efforts to eliminate toxic substances such as PFAS-containing materials and SF6 gas from equipment and processes. Companies are committed to ambitious NetZero goals, focusing on enhancing energy, water, and material efficiency while exploring recycling opportunities for gases like hydrogen and carbon dioxide, as well as processed materials and consumables. Collaborations with equipment and materials suppliers are key to these initiatives, which include refurbishing and reusing components.

Overall, these developments pose significant challenges to the global semiconductor industry across various domains, but also present opportunities for European equipment vendors and their supplier networks.

The overarching goal of equipment development is to lead the world in miniaturisation techniques by providing appropriate products two years ahead of the shrink roadmap of the world’s leading semiconductor device and components manufacturers6. Internationally developed roadmaps such as the International Roadmap for Devices and Systems (IRDS) will also be taken into consideration7. Currently, leading integrated device manufacturers (IDMs) are forecasting a continuation of the technology roadmap following Moore’s law at least until 20298, which corresponds to at least four new generations after the current technology node.

All-in-all, this represents a major challenge to the international semiconductor industry in the areas of lithography, material innovation, processing, assembly, process control, analysis and testing, as well as an opportunity for the well-positioned European equipment vendors and their network of suppliers.

The key focus areas for innovative semiconductor manufacturing equipment technologies are as follows.

Topic 4.1 Wafer fabrication equipment

-

Advanced patterning equipment for sub-2 nm node wafer processing using deep ultraviolet (DUV) and EUV lithography, and corresponding subsystems and infrastructure (e.g. pellicles, masks and resist).

-

Mask manufacturing equipment for sub-2 nm node mask patterning and tuning, defect inspection and repair, metrology and cleaning.

-

Advanced holistic lithography using DUV, EUV and next-generation lithography techniques, such as e-beam and mask-less lithography, directed self-assembly (DSA) and nano-imprinting.

-

In-line wafer inspection and analysis for process control, defect detection, contaminant control etc.

-

Multi-dimensional metrology (MDM) and inspection for sub-2 nm node devices that combine all the spectrum of physical tools and data processing techniques.

-

Thin film processes including thin film and atomic layer deposition, doping and material modification, and corresponding equipment and materials, able to support the increase of binary, ternary and quaternary materials

-

“Bottom up” technologies to selectively deposit materials on topography or on a selected material.

-

Integrated surface preparation, deposition and etch process technologies for optimal interface engineering.

-

Innovative equipment and process strategies for perfect gapfill of metals and dielectrics in decreasing feature sizes.

-

Equipment and manufacturing technology for wet and dry processing, wet and dry etching, including (atomic layer) selective etch processing, thermal treatment, laser annealing and wafer preparation.

-

Increased utilization of AI and modelling (e.g. computational chemistry) techniques for material and process development.

Topic 4.2: Wafer fab equipment for differentiated and/or mature technologies

-

Technologies and tools for the manufacturing and integration of semiconductor components made with advanced nanomaterials and metamaterials (low-thermal-budget-processing 2D materials, nanowires, nanoparticles, quantum dots, etc) with logic and memory technologies.

-

High-volume manufacturing tools for the production of III-V, GaN, SiC or other material substrates of up to 200 mm, or 300 mm in the future.

-

Enable productivity enhancements (e.g. wafer diameter conversions) for heterogeneous integration technologies to significantly improve cost-competitiveness.

-

New manufacturing techniques combining chip and packaging technologies (e.g. chip embedding), which will also require new manufacturing logistics and technologies (e.g. panel moulding).

-

Dedicated equipment for manufacturing of electronics on flexible, structural and/or bio- compatible substrates.

-

New electroplating equipment for ionic liquids (i.e. for Al deposition).

Topic 4.3: Automated manufacturing technologies including fab robotics and wafer transport & handling, required to enable IC-fabs with interconnected tools to support flexible, sustainable, agile and competitive high-volume semiconductor manufacturing9:![]()

-

Enable flexible line management for high-mix and distributed manufacturing lines, including lines for fabrication and deposition of advanced functional (nano) materials.

-

Develop infrastructure technology to interconnect systems from various companies… And anticipate, configure, optimize, etc.

-

Implement fast (and deep) learning as well as semi-automated AI-based decision- making to control processes, to enhance quality, increase reliability, shorten time to stable yield, preserve knowledge and master complexity.

-

Apply Productivity Aware Design (PAD) approaches with a focus on predictive maintenance, virtual metrology, factory simulation and scheduling, wafer-handling automation and the digitisation of the value chain for AI-based decision management.

-

Doubling semiconductor manufacturing in Europe in 2030 also means evolving and upgrading installed base through incremental approaches, which will necessarily mean increased complexity. Managing such hybrid factories will require advanced decision support and diagnosis techniques leveraging GenAI, Retrieval Augmented Generation (RAG) and integrating existing human knowledge and know how.

-

Developing comprehensive modelling and sharing techniques, to enable seamless flow and utilization of information across the whole value chain, will require significant evolution of the existing knowledge management techniques and technologies (NLP to exploit existing documentation, diffusion and sharing of cutting-edge or strategic knowledge).

Topic 4.4: Sustainable semiconductor manufacturing

-

Future innovations should also address new environmentally friendly solutions for manufacturing (e.g. in terms of energy consumption, chemical usage) and environmentally friendly new materials (e.g. in terms of quality, functionality, defects) in parallel with addressing the continued cost of ownership challenges. This will entail, for example, new precursors, chemicals for deposition and other wafer-processing materials, as well as gas delivery, gas handling, pumps and abatement systems. This will also comprise the study and implementation of new solutions for both effluent segregation as described above, including PFAs, as well as for recycling of water and other chemicals.

Major Challenge 5: Advanced packaging, assembly & test equipment solutions

Semiconductor packaging and assembly equipment refers to the machinery and tools used in the process of packaging and assembling integrated circuits (ICs) and other microelectronic devices. Packaging is a crucial part of semiconductor manufacturing as it protects the semiconductor die, connects the chip to a board or other chips, and conducts heat dissipated by the components it contains. It affects power, performance, and cost on both macro and micro levels. The equipment includes various types of machinery from wafer dicing, encapsulation (or moulding) of the die into a plastic package, wire-bonding (on thermal compression, ultrasonic, and stitch bonding), wireless bonding (quasi-monolithic, hybrid bonding) to package marking and labelling equipment.

Semiconductor test equipment is used to evaluate the functionality and performance of semiconductor devices, such as integrated circuits (ICs), during and after the manufacturing process. This equipment is essential for ensuring that the devices meet the required specifications and quality standards before they are shipped to customers. The main types of semiconductor test equipment include Automatic Test Equipment (ATE), Wafer Test Equipment, In-Circuit Test (ICT) etc. These tools are crucial for detecting defects, ensuring reliability, and maintaining high yield rates in semiconductor manufacturing.

1.1.5.4 Major Challenge 5: Advanced packaging, assembly & test equipment solutions

Semiconductor packaging and assembly equipment refers to the machinery and tools used in the process of packaging and assembling integrated circuits (ICs) and other microelectronic devices. Packaging is a crucial part of semiconductor manufacturing as it protects the semiconductor die, connects the chip to a board or other chips, and conducts heat dissipated by the components it contains. It affects power, performance, and cost on both macro and micro levels. The equipment includes various types of machinery from wafer dicing, encapsulation (or moulding) of the die into a plastic package, wire-bonding (on thermal compression, ultrasonic, and stitch bonding), wireless bonding (quasi-monolithic, hybrid bonding) to package marking and labelling equipment.

Semiconductor test equipment is used to evaluate the functionality and performance of semiconductor devices, such as integrated circuits (ICs), during and after the manufacturing process. This equipment is essential for ensuring that the devices meet the required specifications and quality standards before they are shipped to customers. The main types of semiconductor test equipment include Automatic Test Equipment (ATE), Wafer Test Equipment, In-Circuit Test (ICT) etc. These tools are crucial for detecting defects, ensuring reliability, and maintaining high yield rates in semiconductor manufacturing.